- 您现在的位置:买卖IC网 > Sheet目录466 > KAC-9617 (Eastman Kodak Company)IC SENSOR IMAGE VGA 48CLCC

IMAGE SENSOR SOLUTIONS

Functional Description (continued)

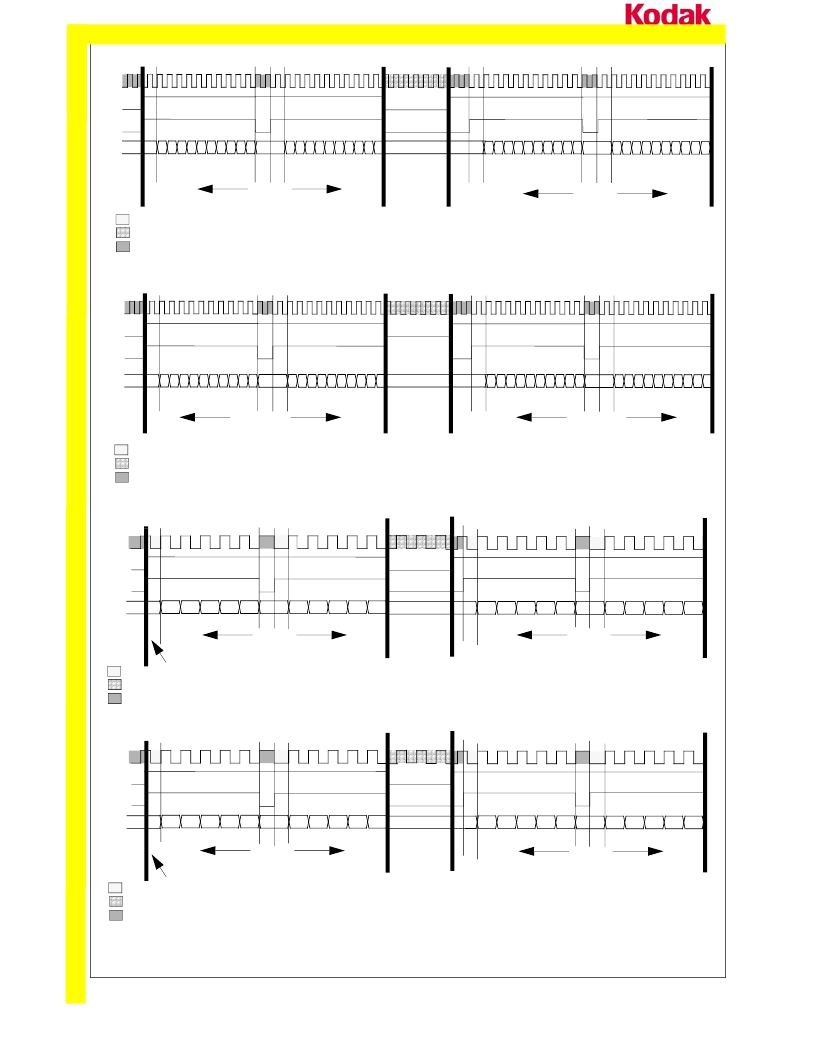

pclk

vsync

hsync

d[11:0]

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row1

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row 2

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row 1

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row 2

frame 1

frame 2

Programmable hsync to 1st valid pixel delay

Programmable inter-frame delay

Programmable row delay

Figure 44. Example of Digital Video Port Timing in Progressive Scan Mode

pclk

vsync

hsync

d[11:0]

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row1

c0 c1 c2 c3 c4 c5 c6 c7 c8 c9

row 3

c0 c1 c2 c3 c4 c5 c6 c7 c8 c 9

row 2

c0 c1 c2 c3 c4 c5 c6 c7 c8 c 9

row 4

Odd Field

Even Field

Programmable hsync to 1st valid pixel delay

Programmable inter-frame delay

Programmable row delay

Figure 45. Example of Digital Video Port Timing in Interlaced Mode

pclk

vsync

hysync

d[11:0]

c 0

c2

c4

c6

c8

c0

c2

c4

c6

c8

c0

c2

c 4

c6

c8

c0

c2

c4

c6

c8

row 1

frame 1

row 3

row 1

frame 2

row 3

Programmable hsync to 1st valid pixel delay

Programmable inter-frame delay

Programmable inter-row delay

Figure 46. Example of Digital Video Port Timing in 2:1 Sub-sampling Mode

pclk

vsync

hsync

d[11:0]

c0

c2

c4

c6

c8

c0

c2

c4

c6

c8

c0

c2

c4

c6

c8

c0

c2

c4

c5

c8

row 1

frame 1

row 2

row 1

frame 2

row 2

Programmable hsync to 1st valid pixel delay

Programmable inter-frame delay

Programmable inter-row delay

Figure 47. Example of Digital Video Port Timing in 4:2 Sub-sampling Mode

www.kodak.com/go/imagers 585-722-4385

24

Email:imagers@kodak.com

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

KAC-9627

IC SENSOR IMAGE VGA 48CLCC

KB-A100SRW

LIGHT BAR 660NM RED 8.89X3.81MM

KB-B100SRW

LIGHT BAR 660NM RED 19.05X3.81MM

KB-C100SRW

LIGHT BAR 660NM RED 8.89X8.89MM

KB-D100SRW

LIGHT BAR 660NM RED 8.89X3.81MM

KB-E100SRW

LIGHT BAR 660NM RED 8.89X3.81MM

KB-F100SRW

LIGHT BAR 660NM RED 19.05X3.81MM

KB-G100SRW

LIGHT BAR 660NM RED 8.89X8.89MM

相关代理商/技术参数

KAC-9618

功能描述:IC SENSOR IMAGE VGA MONO 48-CLCC RoHS:是 类别:传感器,转换器 >> 图像,相机 系列:- 标准包装:480 系列:- 象素大小:6.7µm x 6.7µm 有源象素阵列:768H x 488V 每秒帧数:52 电源电压:3.3V 类型:CMOS 成像 封装/外壳:48-QFP 供应商设备封装:48-QFP 包装:托盘 请注意:* 配用:4H2105-ND - HEADBOARD FOR KAC-004014H2104-ND - KIT EVAL FOR KAC-00401 其它名称:4H20954H2095-NDKAC-00401-CBC-LB-A0

KAC-9618/HEADBOARD

功能描述:HEADBOARD FOR KAC-9618 RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

KAC-9618EVAL-KIT

功能描述:KIT EVALUATION SENSOR KAC-9618 RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

KAC-9619

功能描述:IC SENSOR IMAGE VGA 48-CLCC RoHS:是 类别:传感器,转换器 >> 图像,相机 系列:- 标准包装:480 系列:- 象素大小:6.7µm x 6.7µm 有源象素阵列:768H x 488V 每秒帧数:52 电源电压:3.3V 类型:CMOS 成像 封装/外壳:48-QFP 供应商设备封装:48-QFP 包装:托盘 请注意:* 配用:4H2105-ND - HEADBOARD FOR KAC-004014H2104-ND - KIT EVAL FOR KAC-00401 其它名称:4H20954H2095-NDKAC-00401-CBC-LB-A0

KAC-9619/HEADBOARD

功能描述:HEADBOARD FOR KAC-9619 RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

KAC-9627

功能描述:IC SENSOR IMAGE VGA 48CLCC RoHS:是 类别:传感器,转换器 >> 图像,相机 系列:- 标准包装:480 系列:- 象素大小:6.7µm x 6.7µm 有源象素阵列:768H x 488V 每秒帧数:52 电源电压:3.3V 类型:CMOS 成像 封装/外壳:48-QFP 供应商设备封装:48-QFP 包装:托盘 请注意:* 配用:4H2105-ND - HEADBOARD FOR KAC-004014H2104-ND - KIT EVAL FOR KAC-00401 其它名称:4H20954H2095-NDKAC-00401-CBC-LB-A0

KAC-9627/HEADBOARD

功能描述:HEADBOARD FOR KAC-9627 RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

KAC-9628

功能描述:IC SENSOR IMAGE VGA COLOR 48CLCC RoHS:是 类别:传感器,转换器 >> 图像,相机 系列:- 标准包装:480 系列:- 象素大小:6.7µm x 6.7µm 有源象素阵列:768H x 488V 每秒帧数:52 电源电压:3.3V 类型:CMOS 成像 封装/外壳:48-QFP 供应商设备封装:48-QFP 包装:托盘 请注意:* 配用:4H2105-ND - HEADBOARD FOR KAC-004014H2104-ND - KIT EVAL FOR KAC-00401 其它名称:4H20954H2095-NDKAC-00401-CBC-LB-A0